- El microcodi actua com a microprogramari intern que tradueix les instruccions de la ISA en senyals de control i es pot actualitzar via BIOS/UEFI o sistema operatiu.

- Intel utilitza paquets de microcodi com 20251111, 0x129, 0x12B o 0x12F per corregir inestabilitats de voltatge, millorar estabilitat i mitigar més de 30 vulnerabilitats a múltiples generacions Core i Xeon.

- Les proves mostren que la majoria d'aquestes actualitzacions gairebé no afecten el rendiment, però sí que redueixen penjaments, riscos de degradació i problemes en jocs i càrregues prolongades.

- La complexitat creixent de les CPU i les proves de concepte de codi maliciós a nivell de microcodi converteixen aquesta capa en un nou front crític de seguretat que exigeix monitorització i resposta avançades.

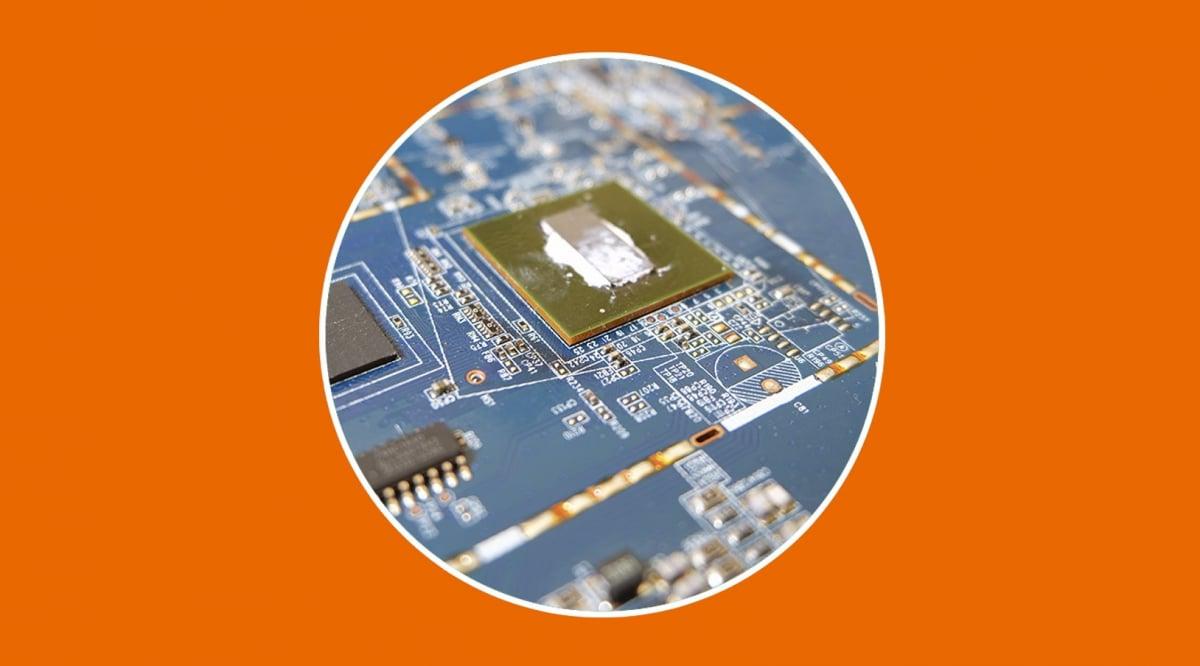

En els últims anys el microcodi de la CPU ha passat de ser un detall fosc per a arquitectes i fabricants a convertir-se en protagonista de titulars sobre rendiment, estabilitat i ciberseguretat. Entre vulnerabilitats tipus Spectre, pegats silenciosos dIntel i proves de concepte de ransomware a nivell de CPU, entendre què passa sota el capó del processador ja no és un caprici tècnic, sinó gairebé una necessitat.

Si mai t'has preguntat per què una simple actualització de BIOS o firmware pot canviar el comportament del teu equip, fer que un joc vagi una mica millor… o que el sistema deixi de penjar-se, la resposta sol ser al microcodi. Desgranarem com funciona, quin paper juga a la unitat de control, com estan gestionant Intel i AMD els seus problemes recents i quins riscos obre el codi maliciós que ataca directament aquesta capa tan crítica.

Unitat de control de la CPU i paper del microcodi

Dins del processador, la Unitat de Control (UC) és la que organitza el treball de totes les altres unitats, una cosa així com el director d'orquestra que decideix què fa cada bloc cicle a cicle. A partir de les instruccions del programa, la UC genera els senyals necessaris per moure dades entre registres, memòria, ALU, FPU i la resta d'unitats funcionals.

Quan arriba, per exemple, una instrucció tipus ADD AX, BX en una arquitectura x86, no és simplement “sumar dues coses i ja”. La UC primer cerca la instrucció en memòria (cicle de buscar), després la descodifica, envia a l'ALU l'ordre de fer una suma binària, especifica que els operands són als registres AX i BX i, una vegada calculat el resultat, habilita l'escriptura a AX per desar el valor final.

Tot aquest flux implica que la unitat de control ha de activar i desactivar accessos de lectura/escriptura a registres, configurar l'operació exacta a l'ALU o FPU (suma, multiplicació, comparacions, etc.) i decidir què es fa amb el resultat. A més, heu de respectar els modes d'encaminament que admeti la CPU i coordinar l'avenç correcte de la seqüència d'instruccions.

La UC també s'encarrega d'aspectes més delicats, com ara distingir entre codi privilegiat i no privilegiat (mode kernel davant de mode usuari), gestionar interrupcions, excepcions i altres esdeveniments asíncrons. En resum, controla tant la lògica funcional com bona part de la lògica de seguretat interna del processador.

A mesura que els processadors s'han tornat més complexos, aquesta unitat ha passat de ser un conjunt relativament senzill de circuits lògics a un sistema molt sofisticat on la manera de generar els senyals de control marca la diferència en rendiment, eficiència energètica i possibilitats dactualització.

Unitats de control cablejades davant de programades

Històricament, els dissenyadors de CPU han optat per dos enfocaments per implementar la unitat de control: la UC cablejada (hardwired) i la UC programada mitjançant microcodi. Cadascuna arrossega avantatges i desavantatges que expliquen per què les arquitectures modernes s'han decantat pel segon camí.

En una unitat de control cablejada, les seqüències de control estan implementades directament en maquinari usant comportes lògiques (AND, OR, NOT), multiplexors, flip-flops i altres. Les connexions entre aquests blocs determinen quins senyals s'activen per a cada instrucció. Aquest disseny sol ser molt ràpid i eficient energèticament, cosa que encaixava bé amb les primeres arquitectures RISC, més simples i amb menys maneres d'operació.

El gran problema de les UCs cablejades és la seva manca de flexibilitat: qualsevol canvi en el comportament del processador obliga a redissenyar el xip i fabricar un nou stepping o fins i tot una nova generació. No hi ha manera senzilla de pegat un bug complex o d'afegir una instrucció nova a posteriori.

L'alternativa és la unitat de control programada, en què el comportament de la CPU es defineix per un microprograma emmagatzemat en una memòria interna (tradicionalment una ROM). Aquest microprograma conté “microinstruccions” que indiquen, per a cada instrucció de la ISA, quins senyals cal activar, en quin ordre i sobre quines unitats funcionals.

Amb una UC programada, el processador pot traduir cada instrucció màquina en una microseqüència de passos elementals: llegir registres concrets, activar l'ALU per a una operació concreta, manejar banderes, escriure de tornada el resultat, etc. Això fa que el disseny sigui més flexible, encara que també més gran, una mica més lent i una mica menys eficient en consum que la versió cablejada pura.

Què és exactament el microcodi de la CPU

El microcodi és, en essència, un microprogramari intern que defineix com la CPU executa les instruccions de la seva ISA. Es tracta d'un conjunt de microinstruccions de nivell molt baix que estableixen quins senyals de control s'han d'activar en cada cicle per materialitzar les operacions que al codi màquina veiem com ADD, MOV, JMP, etc.

Aquesta capa actua com un pont entre el maquinari físic i l'arquitectura de conjunt d'instruccions: per dalt rep instruccions x86, arquitectura ARM, etc., i per sota maneja els detalls concrets de la microarquitectura, com ara el camí de dades, els ports d'execució, la lògica de salts o els registres físics.

Hi ha maneres diferents d'organitzar aquest microprogramari. Al microcodi horitzontal, una única microinstrucció és capaç de generar molts senyals de control en paral·lel i orquestrar diverses unitats funcionals alhora; és molt potent, però ocupa més espai. Al microcodi vertical, cada microinstrucció se centra a controlar una part concreta, reduint l'amplada de la paraula de microcodi a costa de necessitar més passos.

Gràcies al microcodi, el fabricant pot modificar el comportament intern d'un processador sense canviar el silici, sempre que la lògica física admeti les operacions necessàries. Això permet introduir noves instruccions, corregir errors lògics o ajustar polítiques internes, per exemple en l'execució especulativa.

Els processadors moderns, tant CISC com RISC i fins i tot algunes GPUs, integren aquesta capa programable. A més, no tot el microcodi ha de residir en una ROM immutable; una part crítica mínima sol venir de fàbrica per permetre que la CPU arrenqui, però el gruix de les actualitzacions es carrega des de memòries reprogramables durant el boot.

On s'emmagatzema i com s'actualitza el microcodi

A les arquitectures actuals, el microcodi pot estar repartit entre la pròpia CPU i el microprogramari de la placa base. Una part bàsica semmagatzema a linterior del processador, mentre que les actualitzacions es distribueixen a través del BIOS/UEFI o del sistema operatiu, que les carreguen dinàmicament a cada arrencada.

En sistemes x86, el microprogramari de la placa (BIOS/UEFI) pot incloure paquets de microcodi específics per a cada família de CPU. Durant el procés d'arrencada, el microprogramari detecta el model de processador i us injecta el microcodi actualitzat en una memòria tipus flaix o SRAM interna. A partir d?aquell moment, la CPU passa a operar amb la nova lògica.

Els sistemes operatius també hi participen. A Linux, per exemple, les distribucions empaqueten aquests binaris sota el nom de intel-microcode o altres similars, i el kernel els carrega en els primers compassos de l'arrencada. A Windows, el mateix codi es distribueix més tard a través de Windows Update com a actualització de firmware, mitjançant utilitats del fabricant de la placa o amb eines com Intel DSA.

Per manipular aquesta informació es fan servir mecanismes específics com les instruccions RDMSR i WRMSR (Model-Specific Registers), que permeten llegir i escriure a registres interns del processador no accessibles amb el repertori estàndard d'instruccions. A través d'ells, el microprogramari i el sistema operatiu poden ajustar paràmetres fins de configuració, activar mitigacions de seguretat o carregar noves versions de microcodi.

És important tenir en compte que sempre hi ha un microcodi mínim embegut a la CPU que permet arrencar el sistema i aplicar pegats posteriors. Tot i això, el processador no comença a funcionar amb la lògica més recent fins que el BIOS/UEFI o el sistema operatiu carreguen l'últim paquet disponible, per això la insistència dels fabricants a mantenir la BIOS al dia.

Actualitzacions de microcodi: rendiment, estabilitat i seguretat

Una de les grans virtuts del microcodi és que permet corregir errors i afinar el comportament de la CPU postvenda. Quan es publica una nova versió, sol perseguir diversos objectius combinats: millorar el rendiment, solucionar errors funcionals i mitigar vulnerabilitats de seguretat.

En termes de rendiment, un pegat pot reordenar o simplificar les microseqüències d'instruccions conflictives, optimitzar com es fan servir certs ports d'execució, ajustar heurístiques de predicció de salts o modificar prioritats internes de planificació. Tot això sense canviar ni una sola pista metàl·lica del xip.

Pel que fa a la correcció d'errors, el microcodi permet que, davant d'una instrucció concreta o una seqüència d'estats molt particular, la CPU alimenteu rutes alternatives, limiteu accessos privilegiats o forceu neteges de dades sensibles. Això és especialment crític quan es descobreixen bugs que poden donar resultats de càlcul incorrectes o comportaments no deterministes.

El terreny més delicat és la seguretat. Vulnerabilitats com Spectre o Meltdown explotaven detalls de l'execució especulativa i de la gestió de caixets per filtrar informació a través de canals laterals. Part de les mitigacions van passar per introduir canvis de microcodi que alteren com es fan les prediccions, quan es buiden estructures internes o quines barreres s'apliquen entre contextos.

El revers de la moneda és que algunes mitigacions poden penalitzar el rendiment en major o menor mesura, especialment en càrregues de treball molt dependents del comportament especulatiu del processador o de la latència de certs accessos. Per això moltes vegades els pegats arriben acompanyats d'anàlisis detallades d'impacte en benchmarks i aplicacions reals.

Paquet de microcodi Intel 20251111 i les 30 vulnerabilitats

Un exemple recent de la importància d'aquestes actualitzacions el tenim al paquet de microcodi d'Intel identificat com a 20251111. Aquest llançament va coincidir amb un cicle de pegats de seguretat de la companyia, i encara que a GitHub es descrivia com una revisió “no crítica” orientada a millores funcionals i d'estabilitat, la realitat és força més sucosa.

Segons la documentació associada, aquest paquet introdueix correccions funcionals per a múltiples famílies de CPU, millora l'estabilitat en entorns de servidor i amplia el suport per a diverses plataformes Intel Xeon i Core. Però el més rellevant és que forma part del bloc Intel Platform Update (IPU) del novembre, dins del qual s'aborden més de 30 vulnerabilitats diferents.

El patró d'Intel consisteix que el microcodi incorpora les mitigacions a nivell de silici o firmware, mentre que el Security Center publica el mateix dia un lot d'avisos detallant les fallades corregides en capes superiors (firmware, drivers, eines de gestió, etc.). En aquest cas, no es llisten explícitament totes les vulnerabilitats associades a cada canvi de microcodi, però la coincidència temporal deixa poc marge a dubtes.

Entre els canvis documentats apareixen arranjaments per instruccions de cadena com REPSCASB/CMPSB que podien tornar resultats incorrectes, ajustaments en la gestió d'esdeveniments de rendiment a Lunar Lake, correccions d'errors de memòria no corregibles a Emerald Rapids i millores en la detecció d'ASPM L1 en enllaços PCIe de Granite Rapids, entre d'altres punts tècnics.

L'actualització 20251111 afecta un ventall molt ampli de processadors, incloent-hi Intel Core de 12a, 13a i 14a generació, diverses sèries Xeon Scalable de 4a, 5a i 6a generació, així com les famílies Core Ultra 200 V i 200 Series 2, i els nous SoC Xeon 6700P-B i 6500P-B amb nuclis P. En total, s'estima que gairebé 200 models de CPU reben algun tipus de mitigació, cosa que deixa clar l'abast del paquet.

Generacions i steppings afectats pel microcodi 20251111

Si baixem al detall, el llistat de processadors afectats il·lustra fins a quin punt les actualitzacions de microcodi són una peça central de lestratègia de manteniment dIntel. A l'àmbit de consum, trobem diverses famílies Core amb múltiples steppings interns.

Entre els xips descriptori i portàtils, el paquet 20251111 arriba a Alder Lake (12a gen) amb steppings C0, H0, L0 i R0, així com a Raptor Lake (13a gen) en les seves revisions B0, C0 i E0. També cobreix els Raptor Lake Refresh (14a gen) amb steppings C0 i E0, i s'estén als Core Ultra 200 en les variants Arrow Lake (ARL-H i ARL-HX) i Lunar Lake (LNL-P).

A més, s'inclouen processadors de la sèrie Intel N basats en nuclis Gracemont, com ara N95, N100, i3-N305 i N200, que es fan servir amb freqüència en equips compactes i solucions de baix consum. Això mostra que el problema no es limita a la gamma alta, sinó que afecta també productes dentrada i usos embeguts.

A la part de servidors i estacions de treball, el paquet cita de forma explícita a Sapphire Rapids (Xeon Scalable 4a gen) en variants SPR-SP, SPR-XCC i SPR-MCC, a Emerald Rapids (Xeon Scalable 5a gen) amb stepping EMR-SP ia Granite Rapids (Xeon Scalable 6a gen amb nuclis P) en les seves modalitats GNR-AP, GNR-SP i GNR-D.

La llista es completa amb Serra Forest (Xeon Scalable 6a gen amb nuclis E) a l'stepping SRF-SP i amb els SoC Xeon 6700P-B i 6500P-B basats en nuclis P i stepping GNR-D (revisions B0/B1). Tots ells rebran les noves rutines internes encarregades de polir la gestió de voltatges, memòria, PCIe i altres aspectes delicats per a la fiabilitat.

Encara que a Linux les distribucions solen ser les primeres a empaquetar aquestes versions de prova i desplegar-les com intel-microcode, els usuaris de Windows acabaran executant el mateix binari una vegada Microsoft ho validi i ho distribueixi, o quan els fabricants publiquin noves BIOS/UEFI amb el microcodi integrat.

Microcodi i problemes de voltatge a Intel Core 13a i 14a generació

Un altre capítol sonat relacionat amb el microcodi el tenim als bloquejos i inestabilitats detectats en processadors Intel Core de 13a i 14a generació per a sobretaula. Molts usuaris reportaven penjades esporàdiques, pantalles i comportaments erràtics que, després de la investigació d'Intel, es van associar a peticions de voltatge per sobre dels límits recomanats.

L'origen del problema és que, sota certs escenaris, el microcodi i/o la BIOS sol·licitaven nivells de voltatge massa elevats. Per sobre de cert llindar, el processador pot deixar de funcionar de manera fiable, apareixent congelacions o errors de càlcul. Curiosament, els SoC equivalents per a portàtils no es van veure afectats, cosa que apunta diferències en polítiques d'energia i marge tèrmic.

Intel va identificar quatre escenaris principals. El primer passa quan la placa base configura paràmetres de potència per sobre dels valors recomanats; en aquest cas, la pròpia companyia aconsella restablir els ajustaments de potència per defecte a la BIOS. El segon es donava en alguns Core i9 de 13a i 14a generació que mantenien freqüències de rellotge molt altes en molts nuclis fins i tot amb temperatures elevades.

Aquest segon escenari es va mitigar mitjançant l'actualització de microcodi 0x125, que ajusta el comportament de la CPU en condicions tèrmiques exigents. El tercer escenari s'associava al microcodi SVID sol·licitant un voltatge excessiu durant un període perllongat, cosa que desembocava en inestabilitat. Per resoldre'l, Intel va llançar la versió 0x129, que canvia la manera com es negocien aquests nivells de tensió.

El quart escenari problemàtic arribava quan, tant la BIOS com el microcodi, demanaven voltatges relativament alts fins i tot en repòs o amb càrregues molt lleugeres. Aquesta combinació ha estat abordada amb el microcodi 0x12B, que a més inclou les correccions prèvies. Segons Intel, aquesta darrera revisió no comporta una pèrdua de rendiment apreciable i està sent distribuïda coordinadament amb els fabricants de plaques base.

Impacte en rendiment: proves amb els microcodis 0x123, 0x129 i 0x12B

Davant qualsevol pegat de microcodi que toqui voltatge, freqüències o comportament intern, un dubte lògic és si el rendiment es veu afectat de manera visible. Els primers mesuraments sobre processadors com l'Intel Core i9-14900K comparant versions 0x123 i 0x129 mostren diferències mínimes.

A Cinebench 24 multifil, per exemple, el xip obtenia uns 2.136 punts amb el microcodi 0x123, i al voltant de 2.124 punts després d'aplicar 0x129. La caiguda és tan petita que entra fàcilment dins de la variabilitat normal de les proves. A Cinebench R23 multifil, les puntuacions difereixen de forma igualment marginal, amb lleugers balls que es poden atribuir al soroll de mesurament.

Quan es mira els jocs, l'impacte també és molt contingut. Títols com Cyberpunk 2077, executat a 1080p i qualitat mitjana, mostren una pèrdua d'uns pocs FPS (de l'ordre de 236 a 229 FPS en determinats escenaris), cosa que equival a un descens de rendiment d'aproximadament un 2-3% en el pitjor dels casos estudiats.

Altres jocs, com L'ombra del Tomb Raider, només veuen variacions d'un fotograma amunt o avall, cosa tan insignificant que és impossible aïllar-lo de la fluctuació habitual entre passades de benchmark. A canvi, s'observa una notable reducció del voltatge en càrrega i una lleugera millora en temperatures, precisament en la línia del que buscava Intel amb aquestes revisions.

Les investigacions també apunten que el microcodi no altera substancialment el comportament dels nuclis P, centrant-se sobretot en petits ajustaments dels nuclis E i de la gestió denergia. Per a l'usuari final, el balanç és clar: lleugeríssims canvis de rendiment a canvi d'una important millora en estabilitat i reducció del risc de degradació a llarg termini.

Microcodi 0x12F i la inestabilitat de Vmin en sobretaula

Lluny de donar el tema per tancat, Intel ha continuat polint aquestes qüestions amb versions posteriors com la 0x12F, dissenyada per seguir tallant l'anomenada “inestabilitat de desplaçament de Vmin” en processadors Core de 13a i 14a generació de gamma alta, especialment les variants “K” per a sobretaula.

La inestabilitat en qüestió es manifesta sobretot a càrregues lleugeres o de repòs perllongat, típiques de sistemes que romanen encesos durant dies o setmanes amb tasques poc exigents. En aquestes condicions, petites irregularitats en el comportament del regulador de voltatge i la lògica interna poden accelerar la degradació del silici si no es mantenen dins de bandes segures.

Amb el microcodi 0x12F, Intel no canvia la causa arrel del fenomen, però refina encara més la manera com la CPU maneja el voltatge en aquests escenaris de baixa activitat, reduint així el risc d'inestabilitat i allargant potencialment la vida útil del xip. Les proves amb configuracions com un Core i9-14900K i memòria DDR5 5600 MT/s indiquen que no hi ha impacte mesurable en productivitat o jocs.

Per beneficiar-se d'aquestes millores, els usuaris han de actualitzar la BIOS de la placa base a la versió més recent i activar el perfil de “Ajustos predeterminats d'Intel” a UEFI, evitant perfils agressius d'overclocking automàtic. Com a gest addicional, la companyia ha ampliat en dos anys la garantia dels processadors afectats, i ha elevat la cobertura fins a cinc anys en models elegibles.

En resum, la successió de versions 0x125, 0x129, 0x12B i 0x12F il·lustra molt bé com el microcodi ha esdevingut l'eina fonamental d'Intel per ajustar estabilitat, consum i rendiment sense necessitat de llançar revisions físiques dels xips o redissenyar per complet el producte.

Microcodi i baix rendiment en jocs: el cas Core Ultra 200S

Les actualitzacions de microcodi no sempre es limiten a temes de seguretat o fiabilitat; de vegades també apunten directament a millorar el rendiment en escenaris concrets. Un cas interessant és el dels processadors Intel Core Ultra 200S, on es va publicar un nou microcodi (vinculat a la versió 0x114 a BIOS) amb la promesa de millorar entre un 3% i un 8% els FPS en jocs.

Per validar aquestes afirmacions, algunes anàlisis independents es van posar fil a l'agulla amb bancs de proves basats en un Intel Core Ultra 9 285K, una placa ASUS ROG MAXIMUS Z890 APEX, 48 GB de DDR5 a 7.200 MHz, una RTX 4070 Ti SUPER i refrigeració d'alt nivell. Es van repetir les mateixes proves de joc a 1440p amb ajustaments gràfics al màxim abans i després d'actualitzar la BIOS i Windows.

Els resultats van mostrar que, a la pràctica, les diferències de rendiment eren pràcticament inapreciables. Les variacions en FPS es movien en el rang d'unes poques dècimes, perfectament atribuïbles al marge d'error habitual entre passades de benchmark, sense observar els guanys propers al 8% suggerits inicialment.

En aquestes condicions, la conclusió que extreuen alguns analistes és que el nou microcodi, almenys en els títols provats i amb aquesta configuració concreta, no aporta beneficis tangibles en termes de FPS. Això no vol dir que no corregeixi altres problemes interns o que no tingui efecte en jocs o escenaris diferents, però sí posa en relleu que les expectatives de millora de rendiment s'han de prendre amb cautela.

Aquest tipus de casos recorda que el microcodi pot ser una eina molt poderosa per optimitzar el comportament de la CPU, però no fa màgia: està limitat pel maquinari i per la naturalesa de les càrregues de treball. De vegades els canvis són més visibles en estabilitat, consum o latències internes que en el típic més FPS que busca l'usuari gamer.

Complexitat creixent de les CPU i proliferació de bugs

Més enllà de casos concrets d'Intel, hi ha un fenomen de fons: la complexitat dels processadors moderns s'ha disparat, i amb ella el nombre de fallades públiques, errades i vulnerabilitats associades. Ja no parlem de xips senzills, sinó de dispositius amb centenars de milions o milers de milions de transistors, múltiples nuclis, execució especulativa, capes de memòria cau molt profundes i, per descomptat, diverses capes de microcodi.

Analistes com Gabriele Svelto i altres experts han assenyalat que és impossible provar exhaustivament tots els estats interns i combinacions d'instruccions en una CPU daquest calibre. La quantitat d'estats ocults, cues, buffers, taules de predicció i altres estructures fa que algunes fallades només aflorin en condicions molt específiques, de vegades anys després del llançament.

A aquesta dificultat tècnica s'uneix la pressió comercial per reduir els temps de sortida al mercat (time-to-market). Escurçar els cicles de disseny, validació i posada en producció augmenta el risc que bugs complexos arribin als usuaris finals. El microcodi actua aleshores com a xarxa de seguretat parcial, però no pot solucionar absolutament tot.

Per a equips de startups i projectes que treballen a prop del maquinari, aquesta realitat implica la necessitat de reforçar les proves automatitzades, l'observabilitat i la monitorització en producció. Errors que aparentment semblen de programari poden tenir la seva arrel en comportaments atípics del processador, de la memòria o de la interacció entre tots dos.

Per això és clau seguir de prop els butlletins de vulnerabilitats i errades de les arquitectures en què es basa el seu stack, col·laborar amb proveïdors de maquinari i recolzar-se en eines d'anàlisi de fallades reconegudes per la indústria. Casos com Spectre, Meltdown i altres troballes recents al món open source han demostrat que els problemes de CPU no són meres curiositats acadèmiques, sinó vectors d'atac reals que exigeixen una resposta coordinada.

Ransomware i atacs al microcodi: un nou front

L'evolució del codi maliciós també ha posat el focus en el microcodi com a superfície d'atac potencial. Investigacions recents han demostrat que és tècnicament possible modificar el firmware UEFI i carregar microcodi no signat directament a la CPU sota certes condicions, eludint tant antivirus tradicionals com a proteccions del sistema operatiu.

En una prova de concepte centrada en processadors AMD Zen de primera a cinquena generació, se n'explotava una debilitat a l'algoritme de verificació de firmes d'AMD que permetia injectar microcodi no autoritzat. L'experiment de Google va mostrar que era viable alterar, per exemple, la funció de generació de números aleatoris del processador perquè tornés sempre el mateix valor, demostrant un control profund sobre processos interns sensibles.

Tot i que l'exemple de tornar sempre el número 4 pugui semblar anecdòtic, il·lustra que un atacant podria manipular la generació de claus criptogràfiques, la verificació de firmes digitals o els algorismes d'integritat del sistema. I, el més preocupant, aquestes modificacions poden persistir entre reinicis si el vector dactualització de microcodi no està degudament protegit.

Ara com ara, aquests experiments es mantenen en el terreny de la investigació, sense evidències de ransomware operant a nivell de microcodi en entorns reals. Tot i això, obren la porta a un tipus d'amenaça on el propi comportament fonamental de la CPU es torna maliciós, complicant enormement la detecció i la recuperació.

De cara a la defensa, enfocaments com la detecció i resposta esteses (XDR), que combinen anàlisis de comportament avançat i correlació d'esdeveniments a endpoints, xarxes, servidors i núvol, es perfilen com a vies prometedores. La clau és construir una visió holística capaç de detectar patrons anòmals que no encaixen amb el comportament normal de la infraestructura, fins i tot si l'origen últim està en una manipulació del microcodi.

Tot aquest panorama deixa clar que el microcodi ha passat de ser un detall ocult a convertir-se en peça clau per a l'estabilitat, el rendiment i la seguretat de la CPU. Des dels pegats silenciosos que corregeixen desenes de vulnerabilitats fins a les revisions que ajusten voltatges mil·limètricament, passant per les proves de concepte de codi maliciós a nivell de silici, la forma en què fabricants i comunitats gestionin aquesta capa marcarà bona part de la fiabilitat dels sistemes en els propers anys.

Taula de Continguts

- Unitat de control de la CPU i paper del microcodi

- Unitats de control cablejades davant de programades

- Què és exactament el microcodi de la CPU

- On s'emmagatzema i com s'actualitza el microcodi

- Actualitzacions de microcodi: rendiment, estabilitat i seguretat

- Paquet de microcodi Intel 20251111 i les 30 vulnerabilitats

- Generacions i steppings afectats pel microcodi 20251111

- Microcodi i problemes de voltatge a Intel Core 13a i 14a generació

- Impacte en rendiment: proves amb els microcodis 0x123, 0x129 i 0x12B

- Microcodi 0x12F i la inestabilitat de Vmin en sobretaula

- Microcodi i baix rendiment en jocs: el cas Core Ultra 200S

- Complexitat creixent de les CPU i proliferació de bugs

- Ransomware i atacs al microcodi: un nou front